W25Q128JVSIQ vs Alternatives: An Engineering Decision Framework for 2026

Background and Requirement Definition

Before evaluating any specific part number, the engineering team must first define the storage requirements in terms of application context, capacity needs, interface constraints, and cost targets. These parameters determine whether the W25Q128JVSIQ is a reasonable choice or whether a different class of memory would be more appropriate.

The typical application for the W25Q128JVSIQ is MCU firmware storage in embedded systems. Common use cases include consumer IoT devices, industrial controllers, medical instruments, and networking equipment. In these applications, the flash memory holds the main application firmware, a bootloader, and sometimes a second firmware image for over-the-air updates. Configuration parameters and small data logs may also be stored, but they are rarely the primary use case.

The 16 megabyte capacity of the W25Q128JVSIQ is appropriate for a specific range of firmware sizes. A typical RTOS-based application with moderate complexity occupies 2 to 8 megabytes. Adding an OTA backup partition doubles that requirement to 4 to 16 megabytes. Therefore, 16 megabytes is often described as the sweet spot for devices that need both a primary firmware image and a safe backup during OTA updates. If the firmware is smaller than 4 megabytes, a 64 megabit or 32 megabit part would be more cost-effective. If the firmware exceeds 12 megabytes, the 16 megabyte limit becomes a constraint that forces either firmware optimization or migration to a larger part.

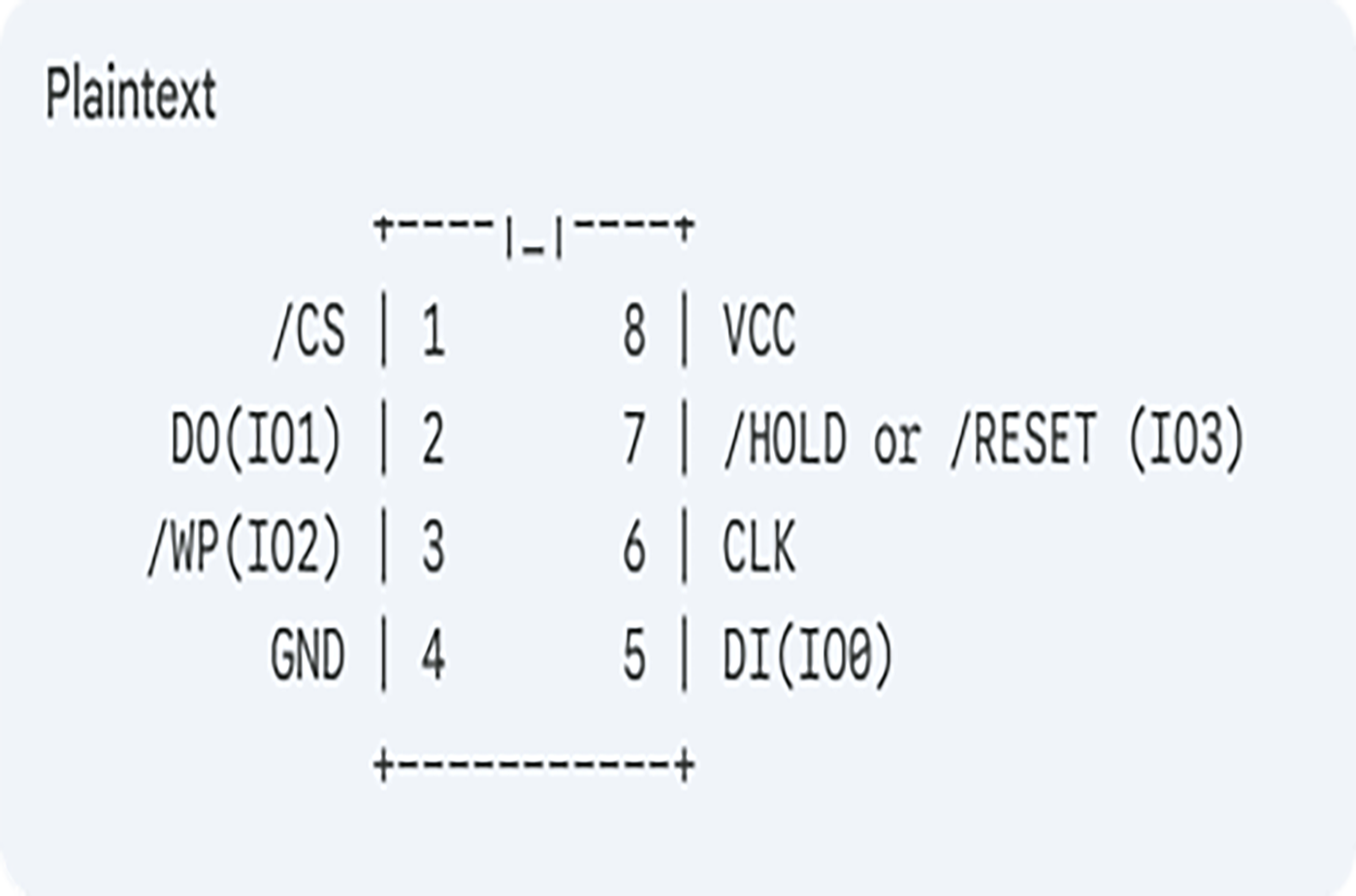

The interface constraint is almost always SPI or Quad SPI. Most microcontrollers in the Cortex-M and Cortex-R families include at least one SPI peripheral, and many include dedicated Quad SPI controllers for external flash. The W25Q128JVSIQ supports both standard SPI and Quad SPI, making it compatible with a wide range of MCUs. The 8-pin SOIC-8 package is also a common constraint because it requires minimal PCB area and is easy to route.

Cost targets vary by application. For consumer products shipping millions of units per year, every penny matters. For industrial or medical devices with lower volumes, reliability and long-term availability are more important than absolute lowest cost.

Candidate Shortlist

Once the requirements are defined, the next step is to identify which memory technologies and specific parts could potentially meet them.

Technology-Level Decision Matrix

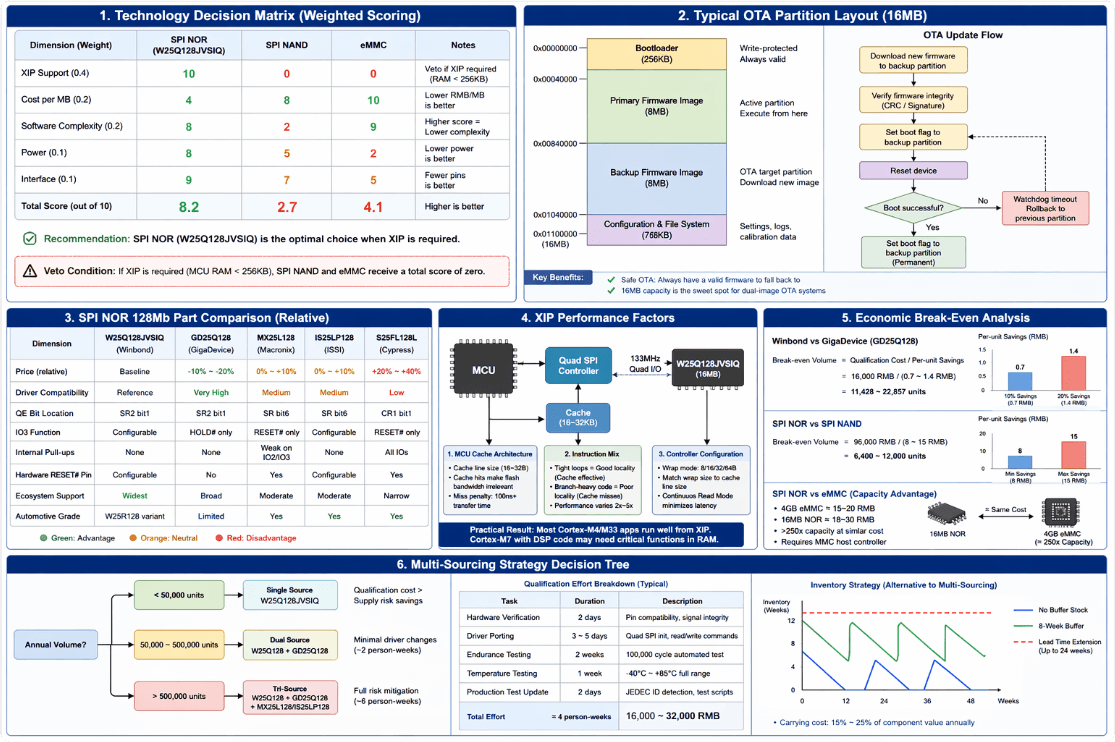

The following matrix quantifies the trade-offs between storage technologies across the dimensions that matter for embedded firmware storage. Each dimension is scored relative to the best-in-class option.

|

Dimension |

SPI NOR (W25Q128JVSIQ) |

SPI NAND |

eMMC |

Decision Weight |

|

XIP support |

Yes |

No |

No |

Critical if RAM < 256KB |

|

Cost per MB (RMB) |

0.75-1.5 |

0.08-0.15 |

0.01-0.03 |

High for consumer |

|

Software complexity |

Low (no ECC) |

High (ECC + bad block) |

Low (controller handles) |

Medium |

|

Random read latency |

<100ns |

>50us |

>100us |

Critical for XIP |

|

Write speed |

Slow (3ms/page) |

Medium |

Fast |

Low for firmware |

|

Power (active/standby) |

15mA / <1uA |

20mA / 10uA |

100mA / 100uA |

High for battery |

|

Interface |

SPI (2-4 pins) |

SPI (4-6 pins) |

MMC (6-10 pins) |

Medium |

Decision Scoring Function

To make the matrix actionable, the following decision scoring function converts qualitative dimensions into a quantitative score. Each dimension is scored from 0 to 10, with 10 being best for the application. The total score determines the recommended technology.

Decision Formula:

|

Total Score = (XIP_Score × 0.4) + (Cost_Score × 0.2) + (Complexity_Score × 0.2) + (Power_Score × 0.1) + (Interface_Score × 0.1) |

Veto Condition: If the application requires XIP (MCU RAM < 256KB, assuming no compression or overlay execution model), then SPI NAND and eMMC receive a total score of zero regardless of other dimensions. XIP is a one-way door decision.

Scoring Guidelines:

|

Dimension |

0-3 (Poor) |

4-6 (Medium) |

7-10 (Good) |

|

XIP |

Not supported |

Partial support |

Full support with cache |

|

Cost per MB |

>1.0 RMB |

0.3-1.0 RMB |

<0.3 RMB |

|

Software complexity |

ECC + bad block + wear leveling |

Basic driver + file system |

Simple read/write commands |

|

Power (active) |

>50mA |

20-50mA |

<20mA |

Part-Level Decision Matrix for SPI NOR

For projects that have determined SPI NOR is appropriate, the following matrix compares the leading 128 megabit parts across dimensions that affect engineering decisions. Scores are relative to the W25Q128JVSIQ as baseline.

|

Dimension |

W25Q128JVSIQ |

GD25Q128 |

MX25L128 |

IS25LP128 |

S25FL128L |

|

Price (relative) |

Baseline |

-10% to -20% |

0% to +10% |

0% to +10% |

+20% to +40% |

|

Driver compatibility |

Reference |

Very high |

Medium |

Medium |

Low |

|

QE bit location |

SR2 bit1 |

SR2 bit1 |

SR bit6 |

SR bit6 |

CR1 bit1 |

|

IO3 function |

Configurable |

HOLD# only |

RESET# only |

Configurable |

RESET# only |

|

Internal pull-ups |

None |

None |

Weak on IO2/IO3 |

None |

All IOs |

|

Hardware RESET pin |

Configurable |

No |

Yes |

Configurable |

Yes |

|

Ecosystem support |

Widest |

Broad |

Moderate |

Moderate |

Narrow |

|

Automotive grade |

W25R128 variant |

Limited |

Yes |

Yes |

Yes |

Constraint-Driven Screening Table

The following table allows engineers to eliminate incompatible parts in under 10 seconds by matching their mandatory requirements against each part's characteristics.

|

If You Require... |

Then Exclude... |

Because... |

|

Hardware RESET# pin on 8-pin package |

GD25Q128 |

RESET# not available on 8-pin package |

|

HOLD# functionality |

MX25L128 |

IO3 implements RESET# only, not HOLD# |

|

No driver changes from Winbond |

MX25L128, IS25LP128 |

QE bit location differs (SR bit6 vs SR2 bit1) |

|

Internal pull-ups on control pins |

W25Q128JVSIQ, GD25Q128, IS25LP128 |

No internal pull-ups; external resistors required |

|

Lowest possible cost |

S25FL128L, MX25L128 |

Price premium of 20-40% or 0-10% |

|

Automotive AEC-Q100 qualification |

Standard W25Q128JVSIQ |

Use W25R128JVSIQ or check alternative grades |

Core Device Analysis

This section analyzes the W25Q128JVSIQ specifically, focusing on engineering trade-offs rather than parameter listing.

System Architecture: OTA Partition Layout

A typical OTA-capable system using the W25Q128JVSIQ partitions the 16 megabyte space as follows. The bootloader resides in the first 256 kilobytes, which is protected from writes during normal operation. The primary firmware image occupies 8 megabytes starting at offset 256 kilobytes. The backup firmware image occupies the next 8 megabytes. The remaining space at the end of the 16 megabyte region stores configuration data and a small file system.

|

Address Range | Size | Content 0x00000000-0x0003FFFF | 256KB | Bootloader (write-protected) 0x00040000-0x0083FFFF | 8MB | Primary firmware image 0x00840000-0x0103FFFF | 8MB | Backup firmware image (OTA target) 0x01040000-0x010FFFFF | 768KB | Configuration and file system |

During an OTA update, the device downloads the new firmware image directly to the backup partition while continuing to execute from the primary partition. After the download completes and the image is verified, the device sets a flag indicating which partition should be booted from on the next reset. The bootloader reads this flag and executes from the designated partition. If the new firmware fails to boot, a watchdog timer triggers a fallback to the previous partition.

This architecture requires approximately 16 megabytes of flash. An 8 megabyte part would force either the elimination of the backup partition, which creates a brick risk during OTA, or reduction of the primary partition size, which limits firmware growth.

XIP Performance: Beyond the Datasheet

The W25Q128JVSIQ supports Quad SPI at 133 MHz, providing up to 66 megabytes per second read throughput. However, XIP performance is not simply a function of flash bandwidth. The actual execution speed depends on three system-level factors that are often overlooked.

First, the MCU's Quad SPI controller and cache architecture dominate XIP performance. When the CPU fetches an instruction, the Quad SPI controller must read from the flash, typically in cache line sized chunks of 16 to 32 bytes. If the code has good locality, cache hits make the flash bandwidth irrelevant. If the code has poor locality, such as large switch statements or scattered function calls, every instruction fetch may miss cache and incur a full flash read latency of several hundred nanoseconds plus the Quad SPI transfer time.

Second, the instruction mix matters. Branch-heavy code with many conditional jumps stresses the prefetch buffer. Tight loops that fit entirely within the cache perform as if running from internal RAM. The practical difference can be a factor of 2 to 5 in execution speed between well-optimized and poorly-optimized code placement.

Third, the Quad SPI controller's configuration affects latency. Some MCUs support XIP with 8, 16, 32, or 64 byte wrap modes. The W25Q128JVSIQ supports all of these through its continuous read mode. Matching the wrap size to the MCU's cache line size minimizes wasted transfers.

For most Cortex-M4 and M33 applications, XIP from the W25Q128JVSIQ provides sufficient performance. For Cortex-M7 applications with branch-heavy DSP code, profiling is recommended to determine whether critical functions should be copied to RAM. A common pattern is to execute the bootloader and initialization code from flash, then copy performance-critical DSP kernels to RAM.

Write Performance and OTA Impact

The page program time is 3 milliseconds typical for a 256-byte page. Writing a full 16 megabyte image using single-byte page program mode requires 16,777,216 bytes divided by 256 bytes per page multiplied by 0.003 seconds, which equals approximately 3 minutes. Using Quad Page Program reduces the time but does not eliminate the fundamental limitation.

In practice, OTA updates are rarely limited by flash write speed. A 16 megabyte firmware image downloaded over a cellular or Wi-Fi connection at 100 kilobits per second takes approximately 20 minutes to download. The 3 minute flash write time adds 15 percent to the total update time, which is acceptable. For updates over a 1 megabit per second local connection, the download takes approximately 2 minutes and the flash write time becomes the dominant factor.

The erase time must also be considered. A full chip erase takes 15 to 30 seconds. However, most OTA implementations erase only the backup partition before writing, not the entire chip. An 8 megabyte partition erase takes 2 to 4 seconds using block erase commands.

Software Abstraction for Multi-Vendor Compatibility

The W25Q128JVSIQ supports the JEDEC standard Read ID command (0x9F), returning 0xEF4018. This allows software to automatically detect which flash part is present. The device also supports SFDP, which allows the kernel to discover its capabilities at runtime.

A practical implication for multi-sourcing is that driver abstraction is straightforward. The following pseudocode illustrates the minimal abstraction layer needed:

|

uint32_t flash_read_id(void) { spi_transfer(0x9F); return (spi_transfer(0) << 16) | (spi_transfer(0) << 8) | spi_transfer(0); } void flash_quad_enable(void) { if (manufacturer_id == 0xEF && device_id == 0x4018) { // Winbond: set SR2 bit1 write_status_register2(0x02); } else if (manufacturer_id == 0xC8 && device_id == 0x4018) { // GigaDevice: same as Winbond write_status_register2(0x02); } else if (manufacturer_id == 0xC2 && device_id == 0x2018) { // Macronix: set SR bit6 write_status_register(0x40); } } |

This abstraction costs approximately 20 lines of code and enables a single firmware binary to support multiple flash vendors. For teams that implement this abstraction, the driver compatibility differences between manufacturers become irrelevant.

Economic Break-Even Analysis

Engineering decisions are ultimately economic decisions. This section provides break-even analysis to quantify when switching from the W25Q128JVSIQ to an alternative technology or supplier becomes financially rational.

Break-Even: Winbond vs GigaDevice

The GD25Q128 is typically 10 to 20 percent cheaper than the W25Q128JVSIQ. At a baseline price of 7 RMB per unit for the Winbond part, the GigaDevice part saves 0.7 to 1.4 RMB per unit. However, switching requires qualification effort.

Assuming qualification costs of 2 person-weeks at an engineering rate of 8,000 RMB per week, the total qualification cost is 16,000 RMB. The break-even volume is calculated as:

|

Break-even volume = Qualification cost / Per-unit savings = 16,000 RMB / 0.7 RMB = 22,857 units (at 10% savings) = 11,428 units (at 20% savings) |

For volumes above 23,000 units annually, switching to the GD25Q128 pays back the qualification investment within the first year. For volumes below 10,000 units annually, staying with the W25Q128JVSIQ is more economical.

Break-Even: SPI NOR vs SPI NAND

SPI NAND offers significantly lower cost per megabyte but requires additional software complexity. A 128 megabyte SPI NAND part costs approximately 10 to 15 RMB, compared to 18 to 30 RMB for a 128 megabyte SPI NOR part. The savings are 8 to 15 RMB per unit.

However, SPI NAND requires ECC and bad block management, adding approximately 3 person-months of engineering effort. At an engineering rate of 8,000 RMB per week, 3 person-months (12 weeks) costs 96,000 RMB.

|

Break-even volume = 96,000 RMB / 8 RMB = 12,000 units (at minimum savings) = 96,000 RMB / 15 RMB = 6,400 units (at maximum savings) |

For volumes above 12,000 units, SPI NAND becomes economically advantageous purely on component cost. However, this analysis assumes the system does not require XIP. If XIP is required, SPI NAND is not an option regardless of volume.

Break-Even: SPI NOR vs eMMC

eMMC offers even lower cost per megabyte than SPI NAND. A 4 gigabyte eMMC part costs approximately 15 to 20 RMB, providing 250 times the capacity of a 16 megabyte NOR part at roughly the same price. For applications that need more than 128 megabytes of storage, eMMC is dramatically cheaper.

However, eMMC requires an MMC host controller, which many low-end MCUs lack. The additional BOM cost of an MCU with MMC interface or an external MMC controller must be factored into the analysis. For systems that already include an application processor with MMC host, eMMC is almost always the correct choice.

Supply Chain Strategy for 2026

The semiconductor supply chain remains volatile in 2026. This section provides a framework for mitigating risk when using the W25Q128JVSIQ.

Current Market Conditions

As of April 2026, lead times for the W25Q128JVSIQ vary significantly by distributor. Some report manufacturer lead times of up to 24 weeks for new orders. Spot market prices have increased accordingly. The primary constraint is wafer fab capacity for mature process nodes, which has been reallocated to AI accelerator chips.

Dual Sourcing Qualification Cost

Qualifying a second source flash part requires engineering effort. A typical qualification includes the following tasks:

- Hardware verification: 2 days to confirm pin compatibility and signal integrity

- Driver porting: 3 to 5 days to adapt Quad SPI initialization and read/write commands

- Endurance testing: 2 weeks of automated cycling to verify 100,000 cycle specification

- Temperature testing: 1 week across -40°C to +85°C range

- Production test update: 2 days to modify test scripts for JEDEC ID detection

Total engineering effort is approximately 4 person-weeks, or 16,000 to 32,000 RMB at typical engineering rates. This cost must be amortized across production volume.

Multi-Sourcing Strategy Recommendation

For volumes below 50,000 units per year, single sourcing the W25Q128JVSIQ is recommended. The qualification cost of a second source exceeds the potential supply risk savings.

For volumes between 50,000 and 500,000 units per year, dual sourcing with the GD25Q128 as a second source is recommended. The GD25Q128 requires minimal driver changes because it shares the QE bit location with Winbond. Qualification effort is approximately 2 person-weeks.

For volumes above 500,000 units per year, tri-sourcing with the W25Q128JVSIQ, GD25Q128, and MX25L128 or IS25LP128 is recommended. The firmware abstraction layer described in Section 3.4 supports all three parts. The qualification effort is approximately 6 person-weeks but provides insurance against allocation from any single supplier.

Inventory Strategy

Holding safety stock is an alternative to multi-sourcing. For a product with 8 week lead time and 12 week manufacturing cycle, holding 8 weeks of buffer inventory insulates production from lead time extensions. The carrying cost of inventory is approximately 15 to 25 percent of component value annually.

Conclusion and Decision Summary

In the context of embedded firmware storage with moderate capacity requirements, XIP support, and OTA update capability, the W25Q128JVSIQ provides a balanced solution across cost, performance, and development complexity.

The decision is justified by exclusion. NAND and eMMC are excluded when XIP is required. Lower capacity NOR parts are excluded when OTA dual partitions are needed. The GD25Q128 is excluded when RESET# is required or volumes are below 23,000 units. The MX25L128 is excluded when HOLD# is required. The S25FL128L is excluded on cost grounds for all but mission-critical applications.

For applications that prioritize ecosystem maturity, reliable performance, and reasonable cost over absolute lowest price or highest capacity, the W25Q128JVSIQ is the appropriate choice.

Frequently Asked Questions (Threshold-Based)

The following answers are structured as decision thresholds rather than explanations. Engineers can use these thresholds to make rapid decisions without reading lengthy background.

Q1: When does NOR stop scaling and NAND become required?

Above 32MB firmware size, or above 1MB per second sustained write workload, or daily OTA frequency exceeding once per day.

Q2: When is GD25Q128 preferred over W25Q128JVSIQ?

Above 23,000 units annual volume, no RESET# requirement, and 2 weeks available for qualification testing

Q3: When is MX25L128 preferred over W25Q128JVSIQ?

When RESET# is required instead of HOLD#, or when internal pull-ups reduce BOM, and driver modification is acceptable.

Q4: When is S25FL128L worth the premium?

When a single field failure costs more than 0.24 RMB per unit times annual volume, or for aerospace/medical/automotive safety applications.

Q5: When is SPI NAND worth the software complexity?

Above 12,000 units annual volume, firmware size above 32MB, and no XIP requirement.

Q6: When is eMMC the right choice?

When MCU already includes MMC host controller, or total storage requirement exceeds 256MB, or cost per MB is the only decision factor.

Q7: When should I multi-source flash parts?

Above 500,000 units annual volume, or when lead times exceed 16 weeks, or when single supplier allocation risk is unacceptable.

Q8: When does XIP become mandatory?

When MCU RAM is below 256KB, assuming no compression or overlay execution model. Above 512KB RAM, copying to RAM is feasible.