What Is W25Q128JVSIQ and Why Does It Dominate Embedded Storage?

The W25Q128JVSIQ is a 128-megabit serial NOR flash memory chip manufactured by Winbond Electronics, a Taiwanese semiconductor company that has become one of the world's leading suppliers of memory solutions. This particular chip belongs to Winbond's widely respected W25Q series, which has been adopted by thousands of hardware designs across consumer electronics, industrial equipment, automotive systems, and communication infrastructure.

What makes the W25Q128JVSIQ truly special is how it balances competing engineering priorities. On one hand, it delivers impressive performance with support for Quad SPI at speeds up to 133 MHz, enabling data transfer rates of 66 MB per second. On the other hand, it maintains a simple 8-pin SOIC-8 footprint that connects easily to almost any microcontroller on the market. It offers 16 megabytes of storage capacity, enough for substantial firmware images and file systems, while consuming less than 1 microampere in power-down mode. It comes from a reputable manufacturer with decades of reliability data, yet it remains affordable for high-volume production.

For embedded engineers, the W25Q128JVSIQ has become something of a default choice. When designers need external flash for firmware storage, configuration parameters, or even execute-in-place code execution, this chip is often the first one they evaluate. Its popularity means extensive community support, readily available reference designs, and reliable supply through multiple distribution channels.

If you are currently selecting memory for an embedded project, click here to request current W25Q128JVSIQ pricing and availability. Our team can help you determine whether this chip fits your technical and budgetary requirements.

Core Specifications Summary

The W25Q128JVSIQ offers a compelling set of specifications that make it suitable for a broad range of applications. Here are the key parameters that engineers typically check first:

- Storage capacity: 128 megabits, which equals 16 megabytes

- Operating voltage: 2.7 volts to 3.6 volts, compatible with 3.3V systems

- Interface support: Standard SPI, Dual SPI, and Quad SPI

- Maximum clock frequency: 133 MHz in all modes

- Maximum data throughput: 66 MB per second in Quad SPI mode

- Package type: SOIC-8 with 208-mil body width

- Operating temperature: -40 degrees Celsius to +85 degrees Celsius, industrial grade

- Data retention: 20 years at typical operating conditions

- Program/erase endurance: 100,000 cycles per sector

Beyond these basic specifications, the W25Q128JVSIQ includes several advanced features that engineers appreciate. It supports hardware and software write protection, allowing designers to protect critical firmware regions from accidental modification. It includes a unique ID that manufacturers can use for device authentication and tracking. It offers flexible erase options including 4-kilobyte sector erase, 32-kilobyte block erase, 64-kilobyte block erase, and full chip erase. These features give developers fine-grained control over how they manage the memory space.

Understanding the W25Q128JVSIQ Part Number Decoder

The part number W25Q128JVSIQ follows a logical naming convention that reveals important characteristics of the device. Once you understand how to read this code, you can quickly identify whether a given Winbond flash chip suits your application without needing to consult the datasheet for every variant.

Here is how the W25Q128JVSIQ part number breaks down:

- W: Winbond, the manufacturer

- 25: Serial flash memory family

- Q: Quad SPI support

- 128: Density in megabits (128 Mbit = 16 MByte)

- J: Generation J silicon (improved over generation F)

- V: Operating voltage (2.7V to 3.6V)

- SIQ: Package, temperature, and configuration (S=SOIC-8, I=industrial, Q=QE bit set to 1)

The generation letter deserves special attention because it affects performance and power consumption. The J generation, represented by the letter J in the part number, operates at up to 133 MHz and consumes less power than the previous F generation, which topped out at 104 MHz. When evaluating used or surplus components, engineers should prefer the J generation unless legacy compatibility requirements force the use of older versions.

The Q suffix at the end indicates that the Quad Enable bit comes preconfigured from the factory with a value of 1. This matters because some Winbond flash chips ship with the QE bit set to 0, requiring the host microcontroller to send a configuration command before Quad SPI mode becomes available. The W25Q128JVSIQ eliminates this step, making it easier to use Quad SPI mode immediately after power-up.

View the complete W25Q128JVSIQ datasheet on our product page for detailed electrical characteristics, timing diagrams, and package dimensions.

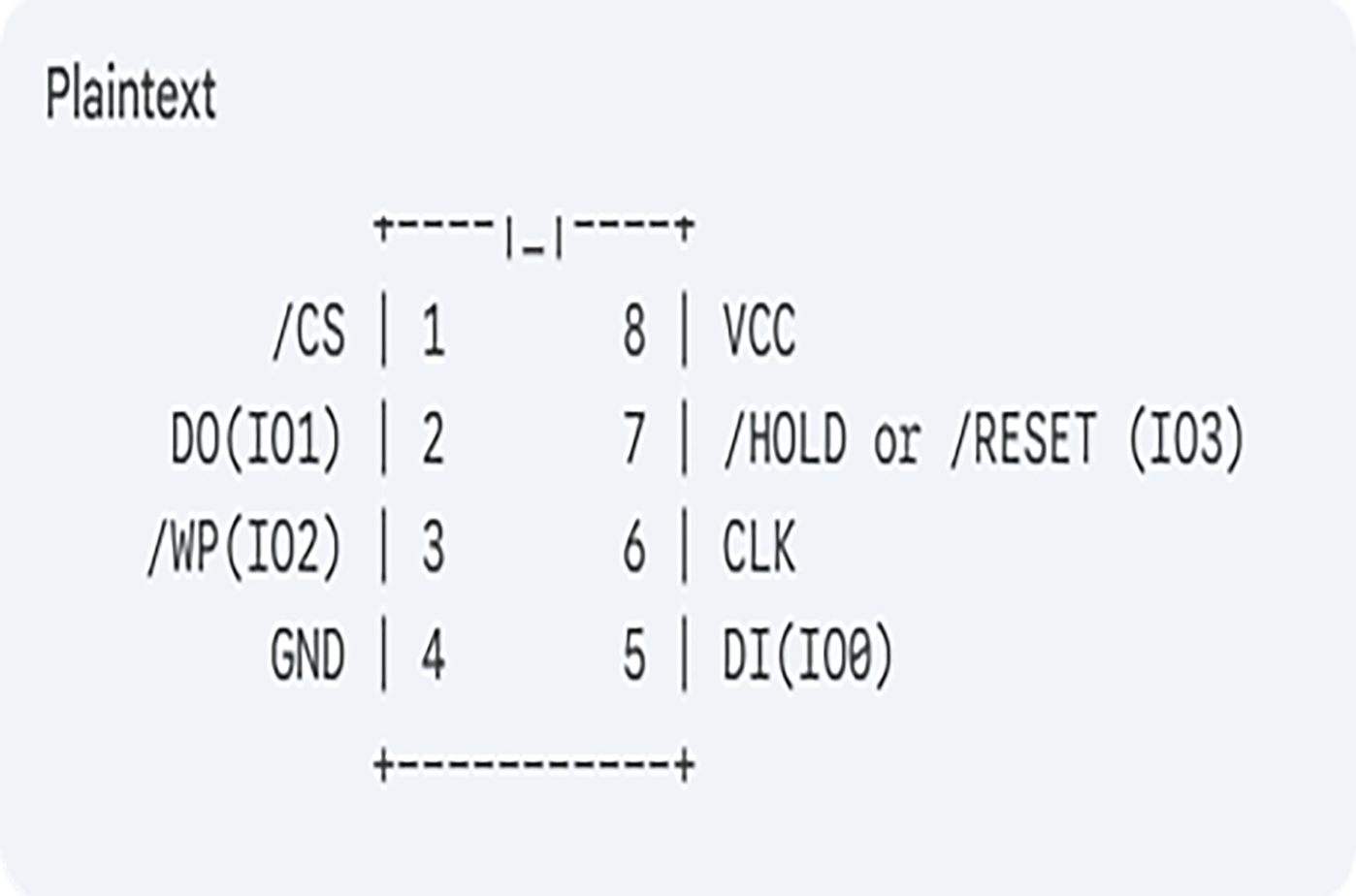

W25Q128JVSIQ Pinout, Connection Guidelines, and Hardware Design Considerations

The W25Q128JVSIQ uses an 8-pin SOIC-8 package, which is one of the smallest and easiest-to-use packages available for external flash memory. This low pin count is a primary reason why SPI NOR flash has largely replaced parallel NOR flash in embedded systems. With only eight pins to route, PCB layout becomes simpler, board area decreases, and manufacturing costs drop.

However, the simplicity of the pinout can be deceptive. Several pins change their behavior depending on whether the chip operates in standard SPI mode or Quad SPI mode. Understanding these differences is essential for correct hardware design.

Complete Pin Function Table

The following table describes each pin on the W25Q128JVSIQ, including its behavior in both standard SPI mode and Quad SPI mode. The mode is controlled by the Quad Enable bit in the status register, which comes preconfigured to 1 on this specific part number.

| Pin Number |

Pin Name |

Standard SPI Function (QE=0) |

Quad SPI Function (QE=1) |

| 1 | CS | Chip select (active low) | Chip select (active low) |

| 2 | DO / IO1 | Data output (serial out) | Bidirectional data pin 1 |

| 3 | WP / IO2 | Write protect input | Bidirectional data pin 2 |

| 4 | GND | Ground | Ground |

| 5 | DI / IO0 | Data input (serial in) | Bidirectional data pin 0 |

| 6 | CLK | Serial clock input | Serial clock input |

| 7 | HOLD / IO3 | Hold input (pause operations) | Bidirectional data pin 3 |

| 8 | VCC | Power supply (2.7V to 3.6V) | Power supply (2.7V to 3.6V) |

A critical observation from this table is that pins 2, 3, 5, and 7 serve dual purposes. When the chip operates in standard SPI mode, these pins provide control functions such as write protection and hold. When the chip operates in Quad SPI mode, these same pins become high-speed bidirectional data lines. This pin sharing is what allows the W25Q128JVSIQ to maintain an 8-pin package while supporting 4-bit wide data transfers.

Essential Hardware Connection Rules

Connecting the W25Q128JVSIQ to a microcontroller requires attention to several details that, if overlooked, can cause intermittent failures or complete non-functionality.

The chip select pin, pin 1, must connect to a GPIO pin on the microcontroller. Even if the SPI bus has only one device, do not tie this pin directly to ground. The chip select pin must be toggled high at the end of each SPI transaction to reset the chip's internal state machine. Leaving it low continuously can cause the chip to misinterpret subsequent clock pulses.

The clock pin, pin 6, should receive special attention during PCB layout. Keep the trace length as short as possible and avoid placing vias on this signal if you can help it. Long clock traces or multiple vias introduce signal reflections and timing skew that become problematic at 133 MHz operation. If your PCB requires a longer clock trace, consider reducing the clock frequency or adding a series termination resistor near the microcontroller.

The power supply pins require proper decoupling. Place a 0.1 microfarad ceramic capacitor as close as possible to pin 8, with the other end connected directly to the ground plane through a short trace or via. For additional noise filtering, add a 10 microfarad electrolytic or ceramic capacitor somewhere on the same power rail. These capacitors filter high-frequency noise from the power supply and provide instantaneous current during switching operations.

The write protect and hold pins, pins 3 and 7, have no internal pull-up resistors. This is a common source of design errors. If you do not need write protection or hold functionality, and if you are not using Quad SPI mode, you must add external pull-up resistors of 4.7 kilohms to 10 kilohms connecting these pins to VCC. Without these pull-ups, the pins float to indeterminate voltages, which may be interpreted as logic lows, inadvertently activating write protection or hold mode. If you are using Quad SPI mode, these pins connect directly to microcontroller GPIO pins that drive them actively, so external pull-ups are not required.

Need help reviewing your W25Q128JVSIQ schematic design? Contact our FAE team for a free design review

Decoupling Capacitor Placement Guidelines

Proper power supply decoupling can mean the difference between a reliable product and one that fails intermittently under temperature extremes or high clock speeds. For the W25Q128JVSIQ, follow these specific guidelines.

Place the 0.1 microfarad ceramic capacitor with a voltage rating of at least 6.3 volts between pin 8 (VCC) and pin 4 (GND). The capacitor should be positioned so that the distance from pin 8 to the capacitor pad is less than 2 millimeters. The via connecting the capacitor's ground pad to the ground plane should be placed immediately adjacent to the pad. This minimizes the loop area and ensures effective high-frequency filtering.

For the 10 microfarad bulk capacitor, placement is less critical but still important. This capacitor can be placed anywhere on the same power distribution network, ideally within a few centimeters of the chip. It provides charge storage for longer duration current transients that occur during program and erase operations.

SPI, Dual SPI, and Quad SPI Modes Explained

The W25Q128JVSIQ supports three distinct operating modes, each offering different trade-offs between pin count, throughput, and software complexity. Understanding these modes allows engineers to select the optimal configuration for their specific application.

Standard SPI Mode Performance and Use Cases

Standard SPI mode uses two dedicated data lines. Pin 5 (DI) serves exclusively as data input from the microcontroller to the flash chip. Pin 2 (DO) serves exclusively as data output from the flash chip to the microcontroller. This separation means no direction switching is required, which simplifies the protocol.

In standard SPI mode, the W25Q128JVSIQ achieves a maximum read speed of approximately 16.6 megabytes per second when operating at the full 133 MHz clock frequency. The calculation is straightforward: 133 million clock cycles per second divided by 8 bits per byte equals 16.625 million bytes per second.

Standard SPI mode is appropriate for applications with modest throughput requirements. Examples include storing configuration parameters, saving sensor data logs, holding bootloader code that runs infrequently, or any scenario where the microcontroller reads from flash only occasionally. The main advantage of standard SPI mode is universal compatibility. Every microcontroller with an SPI peripheral supports this mode without any special configuration.

Dual SPI Mode: Doubling Throughput Without Extra Pins

Dual SPI mode upgrades the data path from one bit to two bits. In this mode, pin 5 (DI) and pin 2 (DO) both become bidirectional data lines, designated as IO0 and IO1 respectively. During a read operation, both pins transmit data simultaneously from the flash chip to the microcontroller. During a write operation, both pins transmit data from the microcontroller to the flash chip.

The throughput doubles compared to standard SPI mode. At 133 MHz, Dual SPI mode achieves approximately 33.2 megabytes per second. The calculation: 133 million clock cycles per second multiplied by 2 bits per cycle divided by 8 bits per byte equals 33.25 million bytes per second.

Enabling Dual SPI mode does not require any hardware changes. The same four pins used for standard SPI mode (CS, CLK, DI, DO) work for Dual SPI mode. The only difference is the command code sent by the microcontroller. Standard SPI read uses command 0x03, while Dual SPI read uses command 0xBB or 0xEB depending on whether the address uses dual mode as well.

Dual SPI mode suits applications that need more speed than standard SPI can provide but cannot afford to lose the hold or write protect functions that Quad SPI mode consumes. It offers a middle ground that many engineers find attractive.

Quad SPI Mode: Maximum Performance for XIP and Fast Boot

Quad SPI mode represents the highest performance configuration available on the W25Q128JVSIQ. In this mode, pins 2, 3, 5, and 7 all become bidirectional data lines, designated as IO0, IO1, IO2, and IO3 respectively. This creates a 4-bit wide data bus.

At 133 MHz, Quad SPI mode achieves approximately 66.5 megabytes per second. The calculation: 133 million clock cycles per second multiplied by 4 bits per cycle divided by 8 bits per byte equals 66.5 million bytes per second. This is four times the throughput of standard SPI mode and twice that of Dual SPI mode.

Quad SPI mode enables a technique called Execute in Place, or XIP. With XIP, the microcontroller maps the external flash memory into its address space and executes code directly from the flash chip without first copying it into internal RAM. This is possible because Quad SPI reads are fast enough to keep pace with the microcontroller's instruction fetch demands. XIP conserves RAM for other uses and can reduce boot times because the system does not need to copy a large firmware image before starting execution.

The W25Q128JVSIQ ships with the QE bit already set to 1, so Quad SPI mode is available immediately after power-up without any configuration commands. This is a significant convenience compared to other flash chips that require an initial configuration step.

[Want to compare Quad SPI performance across different flash manufacturers? Read our detailed selection guide]

Where Engineers Deploy the W25Q128JVSIQ

The W25Q128JVSIQ appears in an extraordinarily wide range of electronic products. Understanding the typical applications helps engineers evaluate whether this chip fits their use case.

Internet of Things Devices

IoT devices represent one of the largest markets for the W25Q128JVSIQ. These products typically include a low-power microcontroller, a wireless connectivity chip such as Wi-Fi or Bluetooth, and external flash for firmware storage. The W25Q128JVSIQ's low power consumption, with standby current below 1 microampere, makes it ideal for battery-powered sensors and wearables. Its 16 megabyte capacity comfortably holds both the main application firmware and over-the-air update images.

Industrial Control Systems

Industrial environments demand components that tolerate temperature extremes, vibration, and long operating hours. The W25Q128JVSIQ's industrial temperature rating of -40°C to +85°C qualifies it for factory automation equipment, programmable logic controllers, motor drives, and human-machine interfaces. The 100,000 program-erase cycle endurance ensures reliable operation even in applications that frequently update configuration data or log operational parameters.

Networking and Communication Equipment

Routers, switches, gateways, and optical network terminals all require flash memory to store their operating system and configuration. The W25Q128JVSIQ appears in many such products because its fast Quad SPI read speeds enable quick boot times. When a router loses power and restores, users expect it to be back online within seconds. The W25Q128JVSIQ helps meet that expectation.

Automotive Electronics

Modern vehicles contain dozens of microcontrollers managing everything from engine control to infotainment. While some automotive applications require specialized AEC-Q100 qualified flash, many non-safety-critical systems can use industrial-grade components like the W25Q128JVSIQ. Dashboard clusters, telematics control units, and advanced driver assistance system cameras all benefit from reliable external flash storage.

Have a specific application in mind? Submit your project requirements for a customized W25Q128JVSIQ recommendation

NOR Flash Versus NAND Flash for Embedded Designs

Engineers new to flash memory often ask whether they should use NOR flash like the W25Q128JVSIQ or NAND flash for their embedded application. The answer depends on how the memory will be used.

When NOR Flash Is the Right Choice

NOR flash excels at random read access and supports Execute in Place. The W25Q128JVSIQ, as a NOR flash device, allows microcontrollers to read individual bytes or words from any address without needing to read entire blocks. This random access capability, combined with fast read speeds, makes XIP practical.

NOR flash also offers superior reliability. It typically has lower bit error rates than NAND flash and does not require error correction code management. For firmware storage, where a single bit error could crash the system, this reliability advantage is decisive.

Choose NOR flash when storing code that the microcontroller executes directly, when read performance matters more than write performance, or when simplicity and reliability are top priorities.

When NAND Flash Might Be Better

NAND flash achieves higher storage densities at lower cost per megabyte than NOR flash. A 128 megabyte NAND chip might cost less than a 16 megabyte NOR chip. This cost advantage makes NAND attractive for data storage applications such as audio recording, image capture, or log file storage.

However, NAND flash has important drawbacks. It cannot execute code directly because it lacks random access capabilities. It requires bad block management because NAND chips inevitably develop defective blocks over time. It needs error correction code to detect and fix bit errors. These complexities add software overhead.

Choose NAND flash when storing large amounts of data, when cost per megabyte is the primary concern, and when the system can tolerate the additional software complexity.

For most embedded firmware storage applications, the W25Q128JVSIQ remains the appropriate choice because its simplicity, reliability, and XIP support align well with the requirements of code storage.

Next Steps in Your Selection Process

After understanding what the W25Q128JVSIQ offers, engineers typically have follow-up questions. How does it compare against alternative parts from other manufacturers? What is the current market price? Where can you buy genuine components with confidence?

These questions lead naturally to the next stage of the decision process. The W25Q128JVSIQ is an excellent chip, but it may not be the best choice for every project. Some applications may benefit from lower-cost alternatives like the GD25Q128 from GigaDevice. Others may require the enhanced reliability features of the Macronix MX25L128. Still others may need the supply chain flexibility of having multiple approved sources.

[Continue reading our detailed comparison: W25Q128JVSIQ vs Alternatives - How to Choose the Right SPI NOR Flash for Your Project]. This companion guide examines competing products side by side and provides a decision framework tailored to different project priorities.

For engineers ready to move forward with procurement, visit our product page for current W25Q128JVSIQ inventory and pricing. For those still evaluating, contact our technical team for application-specific guidance

FAQ Answers

Q1: What is the difference between W25Q128JVSIQ and W25Q128FVSIG?

The J series operates at 133 MHz maximum frequency while the F series tops at 104 MHz. The J series also offers lower power consumption in standby and power-down modes. Pinout and command set are fully compatible.

Q2: Is W25Q128JVSIQ discontinued or obsolete?

No. According to Winbond official product information, the W25Q128JVSIQ remains an active, in-production device. Some distributors may show it as discontinued due to their own inventory policies, but Winbond continues manufacturing this part.

Q3: What does the TR suffix mean in W25Q128JVSIQTR?

TR indicates tape-and-reel packaging for automated assembly equipment. The silicon is identical to the standard SIQ version. TR is used for high-volume production where pick-and-place machines feed from reels.

Q4: What is the zhgs label on W25Q128JVSIQ chips?

Zhgs is a distributor label, not a manufacturer. These are genuine Winbond silicon chips that have been repackaged and relabeled by third-party sellers, commonly found on online marketplaces like AliExpress.

Q5: Can W25Q128JVSIQ replace W25Q128FVSIG directly?

Yes. Both devices share the same SOIC-8 footprint and compatible pinouts. The J series is backward compatible with F series timing. Software may be updated to utilize the higher 133 MHz speed capability.

Q6: How to verify authentic W25Q128JVSIQ?

Read the JEDEC ID using command 0x9F. Genuine chips return 0xEF (Winbond), 0x40 (128Mbit), 0x18 (device ID). Also verify laser-etched markings and test Quad SPI read speeds reaching approximately 66 MB/s.

Q7: What is the lead time for W25Q128JVSIQ?

As of 2026, standard lead times range from 8 to 12 weeks depending on quantity and distributor. The NOR flash market has experienced tight supply. Some distributors maintain spot inventory at premium pricing for urgent requirements.

Q8: Can W25Q128JVSIQ work with 1.8V microcontrollers?

No. The W25Q128JVSIQ requires 2.7V to 3.6V supply. For 1.8V systems, use the W25Q128JWSIQ variant designed for 1.8V operation. Using the 3.3V version would require level shifters on all SPI pins.